# CCSFP-M-SR-MPO-850-70M-DDM

Multi-Mode 100GBASE-SR4 QSFP28 Transceiver

#### Features

- 4 channels full-duplex transceiver modules

- Transmission data rate up to 25Gbps per channel

- Support 40GE and 56GE FDR data rate

- Internal CDR circuits on both receiver and transmitter channels

- Up to 70m on OM3 and 100m on OM4 MMF

- VCSEL array transmitter and PIN array receiver

- Single 3.3V Power Supply

- Operates at 25.78125Gbps per channel

- MPO optical connector

- Digital diagnostic capabilities

- Operating Temperature: Standard: 0°C ~+70°C

- RoHS Compliant

### **Applications**

- IEEE 802.3bm 100GBASE SR4 and 40GBASE SR4

- Infiniband FDR/EDR

#### **Part Number Ordering Information**

|    | Part NO.                                  | Data Rate | Fiber | Distance <sup>*Note1</sup> | Interface | Temp.    |  |

|----|-------------------------------------------|-----------|-------|----------------------------|-----------|----------|--|

|    | CCSFP-M-SR-MPO-850-70M-DDM                | 100Gb/s   | MMF   | 70m/100m                   | MPO       | Standard |  |

| NI | Lata1, ZOm with ON2 MME 100m with ON4 MME |           |       |                            |           |          |  |

Note1: 70m with OM3 MMF, 100m with OM4 MMF.

### **General Description**

CCSFP-M-SR-MPO-850-70M-DDM is a parallel 100Gbps Quad Small Form-factor Pluggable (QSFP) optical module that provides increased port density and total system cost savings. The QSFP full-duplex optical module offers 4 independents transmit and receive channels, each capable of 25.78125Gbps operation for an aggregate bandwidth of 100Gbps 70m on OM3 Multimode Fiber (MMF)and 100m on OM4 MMF. CCSFP-M-SR-MPO-850-70M-DDM is designed with form factor, optical/electrical connection and digital diagnostic interface according to the QSFP Multi-Source Agreement (MSA). It has been designed to meet the harshest external operating conditions including temperature, humidity and EMI interference. The module offers very high functionality and feature integration, accessible via a two-wire serial interface.

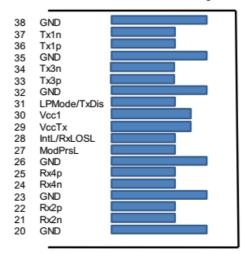

#### **Electrical Connector**

The following figure shows the signal symbols and pad numbering for the module edge connector. The diagram shows the module PCB edge as a top and bottom view, where bottom is nearer the host PCB. There are 38 pads intended for high speed signals, low speed signals, power and ground connections. The module contains a printed circuit board that mates with the electrical connector. The pads are designed for a sequenced mating:

Connected first, disconnected last: - ground contacts Connected second, disconnected second: - power contacts Connected third, disconnected first: - signal contacts

Top Side Viewed From Top

Bottom Side Viewed From Bottom

#### **Pin Description**

| Pad | Logic   | Symbol  | Description                         | Plug Seq. | Note |

|-----|---------|---------|-------------------------------------|-----------|------|

| 1   |         | GND     | Ground                              | 1         | 1    |

| 2   | CML-I   | Tx2n    | Transmitter Inverted Data Input     | 3         |      |

| 3   | CML-I   | Tx2p    | Transmitter Non-Inverted Data Input | 3         |      |

| 4   |         | GND     | Ground                              | 1         | 1    |

| 5   | CML-I   | Tx4n    | Transmitter Inverted Data Input     | 3         |      |

| 6   | CML-I   | Tx4p    | Transmitter Non-Inverted Data Input | 3         |      |

| 7   |         | GND     | Ground                              | 1         | 1    |

| 8   | LVTTL-I | ModSelL | Module Select                       | 3         |      |

| 9   | LVTTL-I | ResetL  | Module Reset                        | 3         |      |

| 10  |         | VccRx   | +3.3V Power Supply Receiver         | 2         | 2    |

| 11 | LVCMOS-I/O | SCL     | Two-wire interface clock            | 3 |   |

|----|------------|---------|-------------------------------------|---|---|

| 12 | LVCMOS-I/O | SDA     | Two-wire interface data             | 3 |   |

| 13 |            | GND     | Ground                              | 1 | 1 |

| 14 | CML-O      | Rx3p    | Receiver Non-Inverted Data Output   | 3 |   |

| 15 | CML-O      | Rx3n    | Receiver Inverted Data Output       | 3 |   |

| 16 |            | GND     | Ground                              | 1 | 1 |

| 17 | CML-O      | Rx1p    | Receiver Non-Inverted Data Output   | 3 |   |

| 18 | CML-O      | Rx1n    | Receiver Inverted Data Output       | 3 |   |

| 19 |            | GND     | Ground                              | 1 | 1 |

| 20 |            | GND     | Ground                              | 1 | 1 |

| 21 | CML-O      | Rx2n    | Receiver Inverted Data Output       | 3 |   |

| 22 | CML-O      | Rx2p    | Receiver Non-Inverted Data Output   | 3 |   |

| 23 |            | GND     | Ground                              | 1 | 1 |

| 24 | CML-O      | Rx4n    | Receiver Inverted Data Output       | 3 |   |

| 25 | CML-O      | Rx4p    | Receiver Non-Inverted Data Output   | 3 |   |

| 26 |            | GND     | Ground                              | 1 | 1 |

| 27 | LVTTL-O    | ModPrsL | Module Present                      | 3 |   |

| 28 | LVTTL-O    | IntL    | Interrupt                           | 3 |   |

| 29 |            | VccTx   | +3.3V Power supply transmitter      | 2 | 2 |

| 30 |            | Vcc1    | +3.3V Power supply                  | 2 | 2 |

| 31 | LVTTL-I    | LPMode  | Low Power Mode                      | 3 |   |

| 32 |            | GND     | Ground                              | 1 | 1 |

| 33 | CML-I      | Тх3р    | Transmitter Non-Inverted Data Input | 3 |   |

| 34 | CML-I      | Tx3n    | Transmitter Inverted Data Input     | 3 |   |

| 35 |            | GND     | Ground                              | 1 | 1 |

| 36 | CML-I      | Tx1p    | Transmitter Non-Inverted Data Input | 3 |   |

| 37 | CML-I      | Tx1n    | Transmitter Inverted Data Input     | 3 |   |

| 38 |            | GND     | Ground                              | 1 | 1 |

Note 1: GND is the symbol for signal and supply (power) common for the module. All are common within the module and all module voltages are referenced to this potential unless otherwise noted. Connect these directly to the host board signal-common ground plane.

Note 2: VccRx, Vcc1 and VccTx are applied concurrently and may be internally connected within the module in any combination.

# Absolute Maximum Ratings

| Parameter           | Symbol          | Min. | Typical | Max. | Unit |

|---------------------|-----------------|------|---------|------|------|

| Storage Temperature | Ts              | -40  |         | +85  | °C   |

| Supply Voltage      | V <sub>CC</sub> | -0.5 |         | 3.6  | V    |

| Relative Humidity   | RH              | 5    |         | 85   | %    |

### **Recommended Operating Environment**

| Parameter                  | Symbol          | Min.  | Typical | Max.  | Unit |

|----------------------------|-----------------|-------|---------|-------|------|

| Case operating Temperature | T <sub>c</sub>  | 0     |         | +70   | °C   |

| Supply Voltage             | V <sub>cc</sub> | 3.135 | 3.3     | 3.465 | V    |

| Power Dissipation          | PMQPM-V4FG-M3   |       |         | 1.5   | W    |

# **Optical and Electrical Characteristics**

| Parameter                                        | Symbol                      | Min   | Тур      | Мах  | Unit | NOTE |

|--------------------------------------------------|-----------------------------|-------|----------|------|------|------|

| Bit Rate Per Lane                                | BR                          |       | 25.78125 |      | Gbps |      |

| Optical Wavelength                               | λ                           | 840   |          | 860  | nm   |      |

|                                                  | Transm                      | itter |          |      |      |      |

| RMS Spectral Width                               |                             |       |          | 0.65 | nm   |      |

| Average Optical Power per Channel                | Pavg                        | -8.4  |          | 2.4  | dBm  |      |

| Transmit OMA, per Lane                           | TX_OMA                      | -6.4  |          | 3    | dBm  |      |

| Laser Off Power Per Channel                      | Poff                        |       |          | -30  | dBm  |      |

| Optical Extinction Ratio                         | ER                          | 3     |          |      | dB   |      |

| Transmitter and dispersion penalty,<br>each lane | TDP                         |       |          | 3.5  | dB   |      |

| Optical Return Loss Tolerance                    | ORL                         |       |          | 12   | dB   |      |

| Output Optical Eye                               | IEEE 802.3ba-2010 Compliant |       |          |      |      |      |

|                                                  | Receiv                      | /er   |          |      |      |      |

| Average Receiver Power per Lane                  | Rxp                         | -9.5  |          | +2.4 | dBm  |      |

| Receiver overload                                | Sat                         | +2.4  |          |      |      |      |

| Damage Threshold                                 |                             | +3.4  |          |      | dBm  |      |

| Receiver Reflectance                             | Rr                          |       |          | -12  | dB   |      |

| LOS De-Assert                                    | LOSD                        |       |          | -7.5 | dBm  |      |

| LOS Assert                                       | LOS <sub>A</sub>            | -30   |          |      | dBm  |      |

| LOS Hysteresis                                   | Hy                          | 0.5   |          |      | dB   |      |

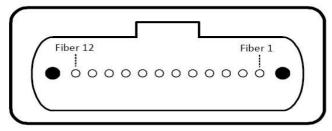

## **Optical Interface Lanes and Assignment**

Below figure shows the orientation of the multi-mode fiber facets of the optical connector

Outside View of the QSFP Module MPO

| Fiber No. | Lane Assignment |

|-----------|-----------------|

| 1         | RX0             |

| 2         | RX1             |

| 3         | RX2             |

| 4         | RX3             |

| 5         | Not Used        |

| 6         | Not Used        |

| 7         | Not Used        |

| 8         | Not Used        |

| 9         | TX3             |

| 10        | TX2             |

| 11        | TX1             |

| 12        | TX0             |

Lane Assignment Table

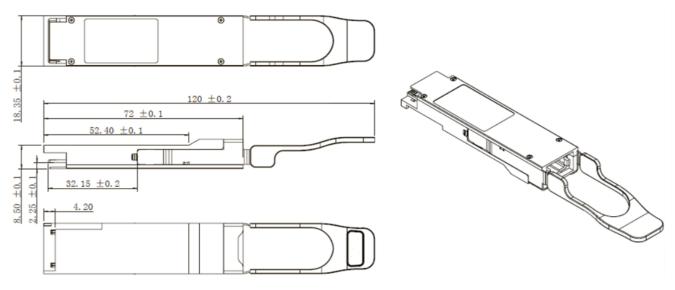

# **Mechanical Specifications**

\*This 2D drawing only for reference, please check with pacific before ordering.